In-vehicle application of high-speed video detection using MPC5200

Car manufacturers are increasingly processing high-speed video images captured inside and outside the car to improve car safety. For example, a camera installed in the vehicle can be used to determine the position of the passenger in the vehicle, so as to configure the airbag in an optimal manner and avoid injury to the passenger. Cameras installed in different positions in the car can also be used for lane departure monitoring, warning before collision, collision avoidance, rear reversing light warning and distance calculation. Many of these applications need to capture video images at a very high rate. Correspondingly, the video images must be processed by real-time complex algorithms to provide feedback for the safety control system in the vehicle. This is a very important task, it can avoid collision, or determine the position of passengers in the car at the moment of collision. Moreover, this technology requires that the engine insulation panel on the driver's side must be able to withstand a high temperature of up to 85 ° C, while other parts of the car need to withstand a high temperature of up to 105 ° C.

------

At present, the challenges facing automakers are to have a cost-effective technology: powerful processing capabilities, rich interfaces, good environmental adaptability and low-power operation. The MPC5200 high-performance embedded processor from Freescale Semiconductor can meet all these design requirements. Its structure is shown in Figure 1.

--- The MPC5200 integrates a high-performance MPC603e core, which can reach 760MIPS processing capacity in the 400MHz operating frequency and -40 ~ 85 ℃ temperature range. High-performance, double-precision floating-point unit (FPU) speeds up complex mathematical operations parallel to other critical tasks .

--- With the help of FPU, MPC5200 processing power can provide enough support for most video detection algorithms. The integrated PCI interface provides a standardized high-speed interface for the CMOS image sensor. The CMOS image sensor can transmit image data to the MPC5200 at a rate of 80 to 100 frames per second, depending on the resolution of the PCI clock and the photo.

--- BestComm intelligent DMA controller can speed up the transfer of camera data to the memory for processing, thereby minimizing the load on the MPC603e main processor core, so that it can be liberated and handle video detection algorithms and other tasks. In addition, the use of the BestComm controller can also reduce the overall interrupt load on the main core, which in turn accelerates the overall throughput. The integrated CAN and J1850 controllers, coupled with external MOST (media-oriented system transmission) support, provide cost-effective integration for the remainder of the automotive safety system and reduce the latency of communicating with these networks.

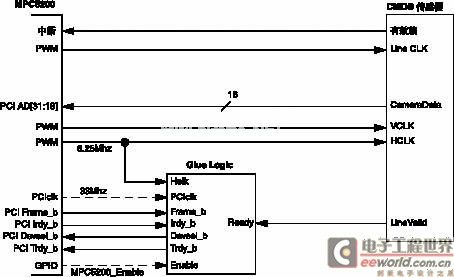

--- The following describes how to design a basic high-speed camera interface circuit for the MPC5200 through the PCI interface. In this example, the Freescale MCM20014 CMOS sensor is used, but other sensors can use almost the same interface mechanism. The interface is very clear and requires less interface logic to complete the connection.

Clock assumption using MPC5200

--- The most likely XLB release target frequency is 132MHz; IPBus is 66MHz; PCIclk (external bus clock) is 66MHz; XTAL's expected input frequency is 33MHz. For this application, the maximum PCI frequency is 33MHz.

In-vehicle application of high-speed video detection using MPC5200

--- The clock ratio between XLB and IPBus, IPBus and PCIclk may be 4: 1, 2: 1 or 1: 1. When XLB is 132MHz, IPBus must be set to 4: 1 or 2: 1 (applicable to 33MHz or 66MHz IPBus respectively). Depending on the IPBus situation (33MHz, 16.5MHz and 33MHz IPBus work together; or 33MHz and 66MHz IPBus work together), PCIclk may support a 1: 1 ratio or a 2: 1 ratio. On the processor side, a 66MHz PCIclk may be used, but the image sensors on the market have not yet reached this speed.

--- If a 50% duty cycle is required, the PWM output value for generating HCLK can only be an even integer quotient of the IPBus clock.

--- The following introduces several possible clock relationships.

--- XTAL: 27MHz, XLB: 108MHz, IPB: 54MHz, PCI: 27MHz, HCLK: 13.5MHz (4/1 ratio PWM from IPBus clock)

--- XTAL: 33 MHz, XLB: 132MHz, IPB: 66MHz, PCI: 33MHz, HCLK: 8.25MHz (8/1 ratio PWM from IPBus clock)

--- The XTAL input can be varied to produce different operating frequencies, but the 8.25 MHz HCLK should be suitable for cameras, and it also provides a 4: 1 difference between the DMA clock and sensor data rate (PCIclk to HCLK). This is helpful for potential bandwidth issues that may occur.

--- The solution is to provide interface logic between the sensor data bus and the PCI data bus. The interface logic of MPC5200 is very simple, but there are still some system application issues that must be seriously considered. One of the matters worth noting is whether to use the PCI bus for other purposes than camera data transmission. If the PCI bus needs to be shared with other devices, the interface logic must coexist with other PCI targets, which requires additional circuitry. If you do not need to share the PCI bus with any other device, the interface logic can assume that any PCI processing is directed at it, so the logic becomes very simple.

--- Figure 2 is the connection diagram of the MPC5200 and the interface chip and CMOS sensor, showing the MPC520 PCI signal connected to the necessary interface logic or directly connected to the sensor. The thick line in Fig. 2 indicates the tri-state. The bus requires an external pull-up resistor, so that in its input value, a logical number "1" appears in the interface logic.

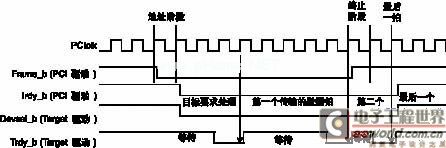

--- The sensor displays in the valid period of its frame: a frame on the sensor is being prepared for transmission. This signal will be connected to the MPC5200 through the IRQ line. Frame transmission needs to be driven by the MPC5200 PCI controller. The signal timing is shown in Figure 3. The specific steps are as follows.

â— MPC5200 PCI makes Frame_b output low level to start processing. The AD line is driven by MPC5200 through address information. Interface logic can ignore this stage.

â— MPC5200 PCI makes Irdy_b output low level to start the data phase. The AD line is still pushed by the MPC5200 until the target (interface logic) judges that Devsel_b "requires" the processing.

â— As long as the target keeps Trdy_b high, the MPC5200 PCI can put the AD bus in one of three states (tri-state) and keep it in a waiting state.

â— On any PCIclk edge that has just appeared, where Trdy_b is detected as low, PCI will capture the data and think that a data beat is to be transmitted.

â— After completing the next to last data beat, MPC5200 PCI makes Frame_b output low, which means that the last data beat is being requested.

â— After the target transmits the last data beat (marked with Trdy_b going low), MPC5200 PCI makes Irdy_b output low level and the processing is completed.

â— There are other signals related to PCI processing, but they are used in the case of PCI transmission errors and are not required in this application.

--- If the ratio of HCLK to PCIclk is 2: 1, then the connection between PCIclk and interface logic is not necessary. If the ratio of PCIclk to HCLK is 4: 1 (people prefer this), a trigger is needed to delay and shorten the duration of the PCI signal Trdy_b.

--- When the 3.3-volt CMOS camera sensor is tri-stated its data bus, the sensor data line is directly and effectively connected to the PCI AD bus. Otherwise, a data Repeater is required in this design. When judging the LineValid signal of the sensor, the sensor should only drive the data line. Figure 4 is a 2: 1 logic relationship diagram of 27MHz PCIclk and 13.5MHz (or similar frequency) HCLK.

--- This example interface only works when no other real PCI target device is connected to the PCI interface. Otherwise, some supported types need to notify the interface logic to respond to the upcoming PCI processing.

--- 33MHz PCIclk and 8.25MHz (or similar frequency) HCLK 2: 1 logic relationship shown in Figure 5.

â— In the case of 2: 1, when HCLK is low, the sensor data is valid, and as HCLK reappears as the next data shot, the next PCIclk edge will capture the data.

--- PCI processing must be performed before LineValid judgment. In PCI processing, when LineValid becomes high, Trdy_b keeps waiting. Since the enable signal of the 5200 requires several cycles to be rejected, additional circuits may be required to close this circuit at the end of the PCI process. In this process, people may request PCI processing of non-cameras (the interface logic must never respond).

â— Since HCLK is derived from MPC5200 PWM, HCLK processing occurs after the edge of PCIclk (according to the design, PCIclk should arrive at the bus in advance).

â— When HCLK falls, Trdy_b's judgment is delayed by one PCIclk.

â— When HCLK rises, Trdy_b also rises immediately.

â— Create a PCI data beat capture on the PCIclk edge, and then create a rising HCLK on the PCIclk edge, because the pixels are constantly increasing.

--- The BestComm task to control sensor data reading is very flexible and can be adjusted according to the size of the sensor. In this example based on Freescale CMOS sensors, the resolution of the sensor is 640 × 480 pixels, 10 bits per pixel. After each line, the pulse stops and the BestComm task will automatically start reading the next line until the entire picture is completed. This method has a very high frame rate, with an overhead of 15 clocks per line.

--- The overhead of transmitting 640 pixel data is 640 clocks, plus the overhead of one line of 15 clocks, the total overhead of transmitting a row of pixels is 655 clocks. Each frame has 480 lines, so the required clock is 655 × 480 = 314400. If a 33MHz PCI clock is used, it takes 9.52ms to transmit each frame of image, that is, 105 frames per second can be transmitted. As can be seen from here, the frame rate depends on the resolution of the clock and sensor.

--- The length and number of pulses read to complete a complete picture are the parameters of BestComm. These parameters can be adjusted according to the type of each sensor. The frame throughput achieved by the interface is much higher than the frame rate of the application. The limiting factor is the computing power required for the algorithm, which is very closely related to the application.

N-NET offer fast Ethernet (10/100M) and Gigabit (10/100/1000M) Ethernet Switches with Managed and Unmanaged style for higher bandwidth, reliability, interoperability and scalability. N-NET Ethernet switches support auto-sense of MDI/MDI-X, facilitating system commissioning and installation. N-NET has over 200 models Options in single mode in dual fiber, multi-mode in dual fiber, and single mode in single fiber. Low power consumption, reliable and stable performance.

Network Switch,POE Switch,Gigabit Switch, Ethernet Switch

Shenzhen N-net High-Tech Co.,Ltd , http://www.nnetswitch.com