1 Introduction

The establishment of the chip model is an effective method for early chip architecture decision-making. Modeling can not only analyze the performance of the chip, but also develop the software before the hardware is completed, which not only improves the product success rate, but also shortens the development cycle. Designers used C/C++ language for hardware modeling early. However, with the increase of hardware and software complexity, the C/C++ language is difficult to meet the requirements. OSCI introduced the SystemC language in time to adapt to new demands. SystemC has been widely used in SoC software and hardware modeling.

At present, most of the documentation on SystemC modeling is the author's description of the overall model of the chip he designed. Although the literature for specific chip design has reference value, the model itself has limited reference. On the other hand, the basic components that make up SoC hardware have better modelability for their model design because of their reusability. The research results in this area are relatively few, and focus on the bus modeling, you can also see the modeling method in multi-core design.

In addition to the above bus and CPU architecture, on-chip or off-chip memory is also a key module of the system, which has a crucial impact on system performance. The [6] extended the SystemClick framework to analyze the impact of shared memory on performance through the memory model. Literature [7] models multi-channel DRAM and analyzes the impact of different configurations and usage on performance. Both of these documents have a detailed analysis of the designed model, which has good reference value, but the versatility of the two is not good. This paper presents a configurable general-purpose memory SystemC model.

2 SystemC

SystemC can be viewed as an extension of C++ hardware modeling and simulation, especially for integrated circuit modeling, but it can actually be used to describe more systems. SystemC defines a mechanism for handling parallel events and simulation time by determining the simulaTIon kernel algorithm. SystemC also defines modules, ports, interfaces, channels, and other concepts to form a complex SoC connection relationship and hierarchy. Therefore, it solves the problem of standard C++ language for complex hardware modeling.

3 Memory modeling

3.1 Memory Model Overview

To help designers analyze system performance and select the most appropriate memory architecture, the memory model needs to reflect the key parameters that impact performance, namely bandwidth, latency, and arbitration mechanisms. These parameters are determined by the structure of the memory and other parameters. On the other hand, this article hopes to propose a general memory model, so there will be more parameters for configuring memory to simulate a particular type of memory feature, such as multi-port SRAM.

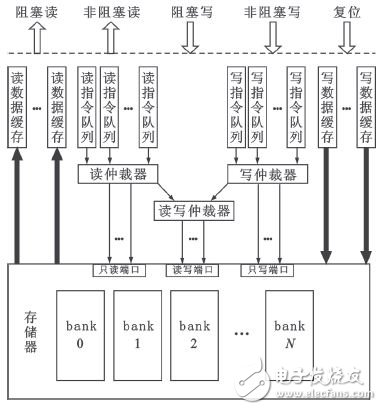

Figure 1 shows the structure of the designed memory model. It consists of three parts: one is the model interface; the other is the port and bank configurable memory; the third is the memory controller consisting of read and write channels and arbitration mechanism. The interface part uses transaction-level modeling, while the internal module uses clock-accurate modeling, which facilitates interface connection and improves simulation speed while ensuring time accuracy.

Figure 1 configurable memory model structure

3.2 Memory Interface

SystemC-based memory model interface, derived from the interface base class defined by SystemC. The entire memory model is a SystemC module that becomes the hierarchal channel in the SystemC concept by implementing the defined memory model interface. Therefore, the memory model will be used as a basic component to connect other modules as other SystemC defined channels, such as FIFOs, to construct a SoC hardware system. The designed memory has a transaction level SystemC interface as described below.

Blocking read interface: This interface is used to read a given size of data at a given address. When the data is not read, the module thread calling this interface will be blocked until the data is read. In addition to the address and data, the interface also contains the caller's flag information.

Non-blocking read interface: Unlike the blocking read interface, if the read command cannot be accepted at the time of the call, it returns a failure. Otherwise, it will exit successfully without waiting for the data to return. The module thread that invokes the interface in this way can do other things while waiting. The current read data broadcast by the caller by listening to the memory model corresponds to the caller flag to read the data later.

Blocked Write Interface: This interface is used to write a given size of data to a given address in memory. When an instruction or write data cannot be received by the memory model, the called thread is blocked until it is accepted. In addition to the address and data, the interface also contains the caller's flag information.

Non-blocking write interface: Unlike a blocked write interface, when an instruction or data cannot be accepted, it returns a failure without waiting. Otherwise it returns successfully.

Reset interface: Used to reset the memory model.

In order not to require externally providing the clock required by the memory model, the clock input is not included in the memory model interface. There is a dedicated clock generation thread inside the model.

According to the area of the screen body, the column display is divided into two types: single column and double column: mostly used for outdoor advertising, with a wide field of vision and relatively empty surroundings, such as squares, parking lots, and traffic intersections. In addition to the steel structure of the screen body, the column type also needs to be made of concrete or steel columns, which must mainly consider the geological conditions of the foundation.

In terms of Indoor Led Display area, the design of its steel structure should consider factors such as foundation, wind load, earthquake magnitude, water resistance, dust resistance, ambient temperature, and lightning protection. Auxiliary equipment such as lighting, as well as maintenance facilities such as roads and ladders. The entire outdoor screen structure must meet the protection level above IP65.

Fixed column LED display,Outdoor Column Mounting LED Display,Pillar Support LED Display,Single column LED display

Shenzhen Vision Display Technology Co,.LTD , https://www.ledvdi.com