Luke Miller was not an advocate of HLS (High Level Synthesis) in the first place. When using the early version of the tool, he seems to have had some bad experiences. He wrote: "...My heart builds a wall, I need help." Fortunately, he seems to have passed a 12-step HLS training event, and now he can work effectively with Xilinx Vivado HLS.

SemiWiki has a new blogger called "The FPGA Expert." Through a simple search from LinkedIn, I learned that the FPGA expert is Luke Miller, who recently published a blog post on how to use High Level Synthesis (HLS) to develop various acceleration hardware from C to other HLL versions. Although not as detailed as the "hands-on recipe", it is still very interesting.

Miller has worked as an ASIC designer at IBM, a hardware engineer (engineer/architect) at Lockheed, and is currently a PE with military and aerospace design experience. Miller's website, called FPGA Expert, has a special video about its personal experience that describes a number of military, aerospace, and medical projects (aircraft, radar, and medical imaging), so I guess he should have a very rich FPGA design experience. His website confirmed this conjecture. Miller also seems to know HLS very well. He wrote:

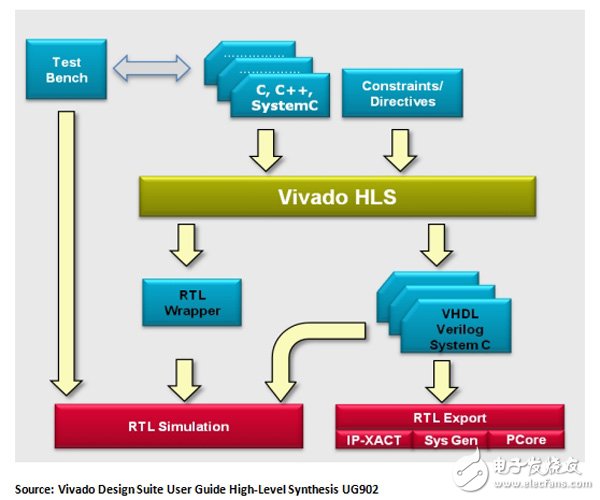

“Design time acceleration is not a conversion from C to VHDL. The real key factor is the simulation domain—you no longer need to verify each design piece by piece through RTL.â€

Luke Miller is not always an advocate of HLS (High Level Integration). When using an early version of the tool, he seemed to have a bad experience. . He wrote: "...My heart builds a heart wall, I need help." Fortunately, he seems to have passed a 12-step HLS training event, and now he can work effectively with Xilinx Vivado HLS.

Click here to read Miller's advice on HLS: "High Level Synthesis – It's for Real" â€%96-%92s-real.html

The following is the full text of Miller for reference:

=========================================================== =============================================

High Level Synthesis – It's for Real

By

theFPGAexpert

Published on 04-11-2013 06:30 PM

It was spring 2010 and I was asked to attend an HLS (High Level Synthesis) meeTIng. To be honest I cringed, after my bad relaTIonship with Accel DSP and broken promises my heart was all walled up and needed counseling. But my management had a Way of making me an offer I could not refuse, like keeping my job. So reluctantly I went. Does your employer do lunch and learns instead of real training? You know what that equals right? A 1/8 pay cut, but let's play Nice.

I'm after the usual introducTIons at the meeTIng they began to get into the meat of the tool. I quickly diverted and asked if we could see the tool in action and move away from the power point and boy did they. First up was a cookie cutter FIR filter but it worked, really! Then they moved into floating point designs etc. This HLS was the greatest thing since sliced ​​bread. I saw its potential and I needed to try it. We all agreed on an evaluation period. Now I am by No means the best coder in the world, but even the best would have a hard time beating the HLS tool with respect to design time, area and latency.

What HLS is not: It is not a coder in a box, thus sit down the software guy and have him designing FPGAs. You need to understand the FPGA, no exceptions or you will have a fat, slow design. The C or its variant Will need to be restructured, smartly, thus helping the tool out so it can perform better. It is not a button you press and you have a bit image. I know how program managers think.

I see it as Xilinx Corgen on steroids which are driven by a C file. The speed up in design time is not in the translation from C to VHDL but really is in the simulation domain. You are no For example, I design a Beamfomer in C. I compile it and then run 'a.exe' and verify that the answer matches the expects. That took about a second. For many PRIs of data That could of taken hours in ModelSim. Catching on? I then bring up the HLS tool and pull in the C file and the tool reports the latency, area, clock frequency etc. From that information I can determine which FPGA to use. I then I used to improve the area / latency by using unrolls and pipeline directives. About an hour later my beamformer is done. I then simulate the RTL at my top level but I already know the math works and the tool took care of the boundary conditions The goal of this article is by no means a recipe on HLS usa Ge but hopefully entices you to check it out, you won't be sorry.

60FT Monopole Tower

Product Description

Available height:5-80m

Electric pressure:10kv--550kv

Material:Q345B/A572,minimum yield strength>=345MPA,

Q235B/A36,minimum yield strength>=235MPA

Galvanized:Hot dip galvanization,thickness is>=12um

Delivery lead time:30 days after receiving 30% deposit

Lifetime:Minimum 25 years

Structure:Overlap connection/Flange connection

Galvanizing standard:EN ISO 146,ASTM/A123

Manufacturing and workmanship:BS449 or AISC

Welding standard:BSEN287,BSEN288 or equivalent

Telecommunication Monopole,Palm Tree Monopole,Supply Power Transmission Monopole,60FT Monopole

YIXING FUTAO METAL STRUCTURAL UNIT CO.,LTD( YIXING HONGSHENGYUAN ELECTRIC POWER FACILITIES CO.,LTD.) , https://www.chinasteelpole.com