Overview

The most common use of high-level synthesis design is to create an accelerator for the CPU, moving the code executed in the CPU to the FPGA programmable logic to improve performance. This article shows how to use HLS IP in a Zynq AP SoC design.

Apply Vivado HLS IP to Zynq Devices

This integrates HLS IP and software drivers created by HLS to control the IP design implemented on Zynq devices.

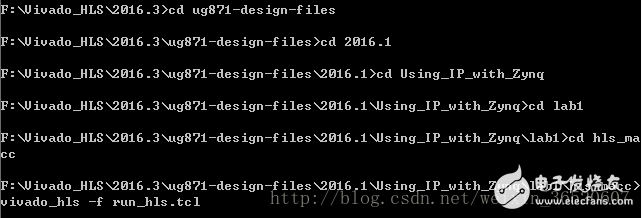

Step 1: Create a Vivado HLS IP Block

When the script completes, it generates a vhls_prj file containing the HLS IP. Here's how the Vivado HLS IP blocks are integrated into the Zynq device using IP Integrator.

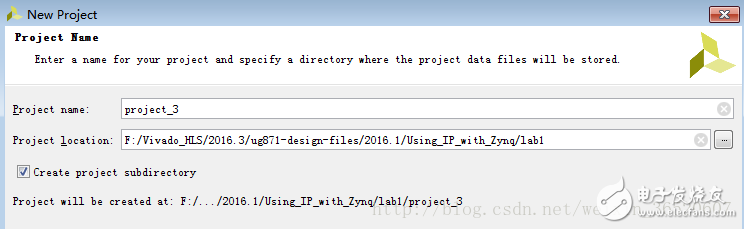

Step 2: Create the Vivado Zynq Project

1. Open vivado 2016.3, click Create New Project, select the Using_IP_with_Zynq\lab1 path, and then select RTL Project and Do not specify sources at this TIme on the Project Type page.

Then select ZYNQ-7 ZC702 EvaluaTIon Board under Boards, and finally click Finish.

Step 3: Add HLS IP to the IP Catalog

Click on the IP Catalog in the Flow Navigator window, then click on IP SetTIngs, in the IP section Add Repository, select Using_IP_with_Zynq\lab1\hls_macc\vhls_prj\soluTIon1\impl\ip, and add the HLS_macc HLS IP to the IP directory.

Step 4: Create a design for the IP Integrator Block system

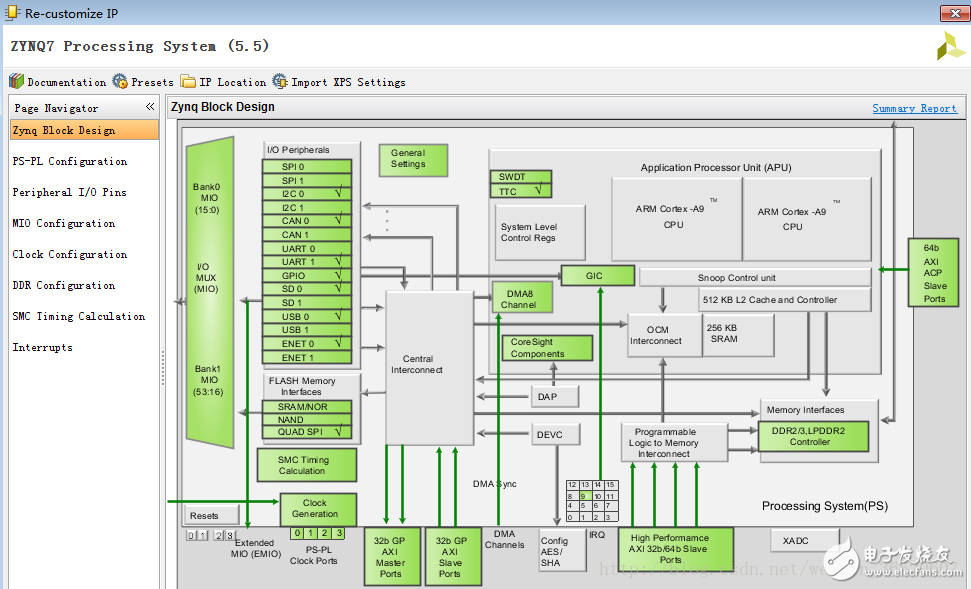

1. Click Create Block Design in the Flow Navigator window, change the design name to Zynq_Design, then add the ZYNQ7 Processing System IP, then double-click ZYNQ IP to open the Re-customize IP window, select ZC702 in Presets, and click MIO Configuration in the Page Navigator window. Expand Application Processor Unit, remove Timer 0, and finally click Interrupts in the Page Navigator window, check and expand Fabric Interrupts, select IRQ_F2P[15:0]

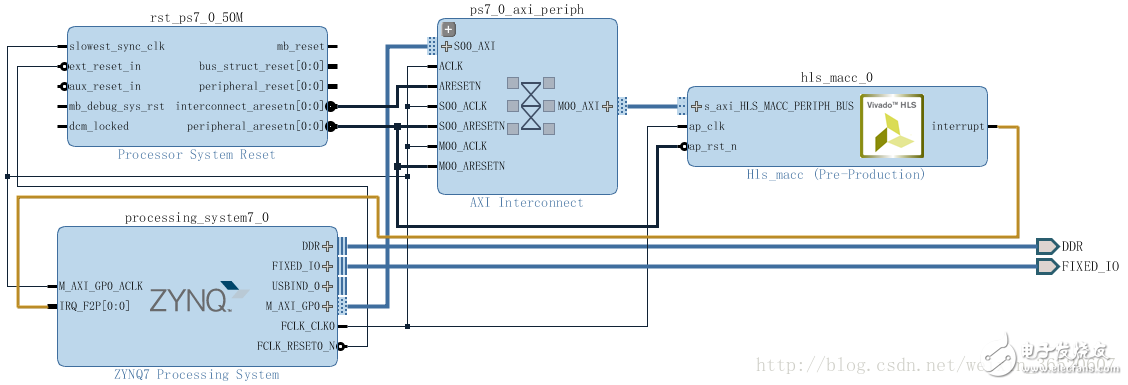

2. Click Run Block Automation on the title, select processing_system7_0, remove Apply Board Presets, then add hls_macc IP to the design, then click Run Connection Automation, select /hls_macc_0/S_AXI_HLS_MACC_PERIPH_BUS, so the HLS IP is automatically connected to M_AXI_GP0 on the Zynq device. The interface then connects the interrupt port of hls_macc_0 with the IRQ_F2P[0:0] port of PS7.

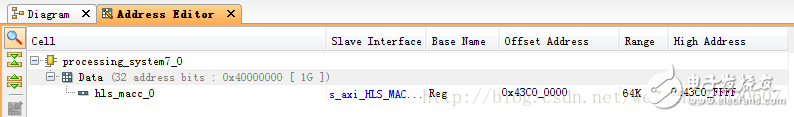

3. Select Address Editor and make sure that hls_macc_0 has been assigned to the main address range. If not, click Auto Assign Address.

Finally, Validate Design, after the success, save the Block Design.

Step 5: Implement the system

Before further system design, a source and HDL wrapper must be generated as a synthesis and implementation top-level function.

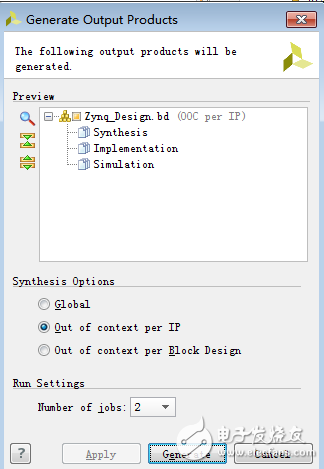

1. Select Project Manager in the Flow Navigator window, right-click on Zynq_Design and select Generate Output Products, then select Generate to start generating the necessary source files.

2. Right-click on Zynq_Design and select Create HDL Wrapper. The top level of Design Sources becomes the Zynq_Design_wrapper.v file. Now the design is ready to be integrated and implemented, and the FPGA programming bitstream is generated.

3. Click Generate Bitstream. When the bitstream is complete, select Open Implemented Design in the pop-up dialog box and click OK.

Step 6: Software development and running on the Zynq system

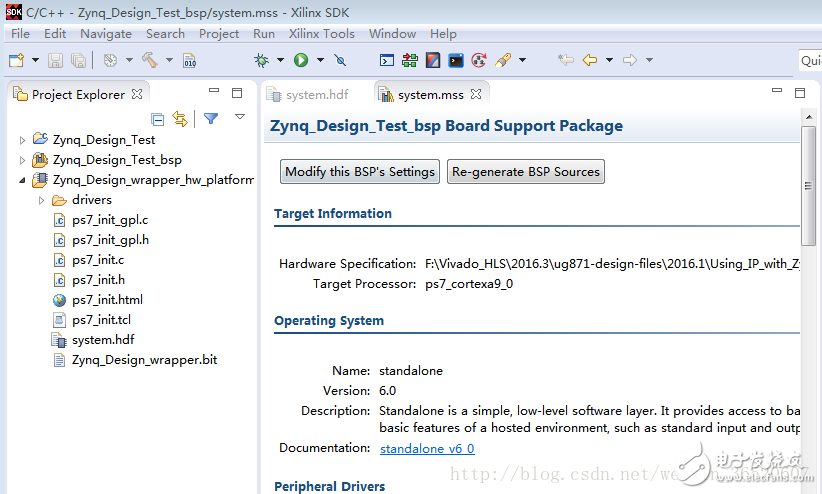

Now we are ready to import the design into the Xilinx SDK. In the SDK, you will create the software (if any) that runs on the zc702 board. The driver for the HLS block is generated during the HLS export to the Vivado IP encapsulation. This driver must be available in the SDK so that the PS7 software can communicate with the block.

1. In the Vivado File menu, select Export > Export Hardware, and check Include Bitstream, then select Launch SDK from the Vivado File menu.

2. In the SDK File directory, select New > Application Project, enter Zynq_Design_Test in the project name, click next, select Hello World, and click finish. Power up the zc702 board here and test the HelloWorld application, make sure all the boards are properly connected, download the bitstream files on the FPGA device, and see the documentation on the zc702 development board.

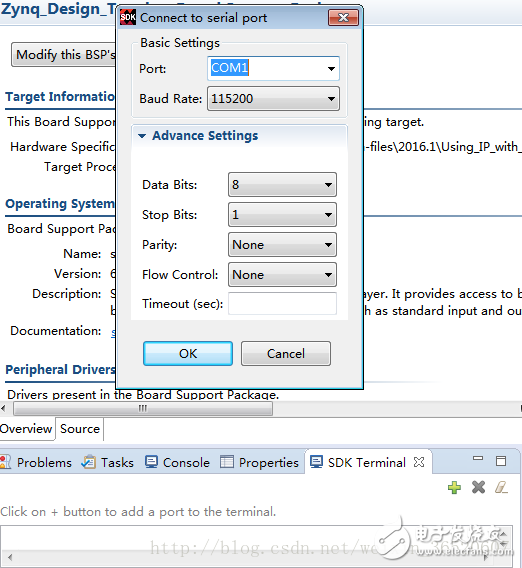

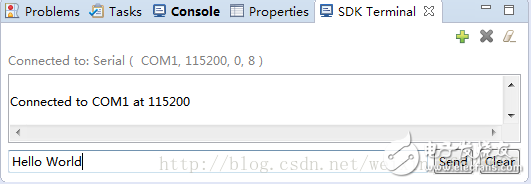

3. Select Xilinx Tools > Program FPGA, notice that the Done LED is lit, then click the SDK Terminal in the bottom window, select Connection to Serial port, select COM1 for Port, select 115200 for Baud Rate, click OK.

4. Right-click Zynq_Design_Test and select Run As > Launch on Hardware. Finally, verify that Hello World is accepted in the Terminal window.

to sum up

This article describes how to create a Vivado HLS IP using Tcl scripts and import the HLS IP design IP into IP Integrator and how to connect the HLS IP to a Zynq AP SoC using the AXI4-Lite interface and the AXI4-Stream interface.

We produce Lighting for commerical ,industrial ,and household . Specially for desk lamp LED which 360 degree bent freely .It can brighten you in any angle as

you want. Road light and functional light also.

Home Outdoor Lighting LED Stadium Light LED Floodlight LED Tri-proof Light LED Street Light LED Garden Light LED Canopy Light Indoor Lighting LED Panel Light LED Batten Light GL Series LED Batten Light GLK Series LED Batten Light

Home Lighting & Furnishings - Quality, Style and Selection. Lamps Plus offers a complete selection of indoor and outdoor lighting fixtures. From stylish ceiling light fixtures, chandeliers and trend-setting ceiling fans to thousands of designer lamps and lamp shades that are in-stock and ready to ship.

Home Light,Led Desk Lamp,Rgb Night Lamp,Bathroom Lights

Jiangmen soundrace electronics and technology co.,ltd. , https://www.soundracegroup.com